内存主导半导体行业,同时推动封装工艺发展

2019年的Semicon大会上曝出不少有趣的消息。曾供职于英特尔、目前效力于Doller咨询集团的Ed Doller表示,目前生产出的大多数晶体管都被用于内存技术领域,特别是DRAM与NAND闪存。下图为他发给我的VLSI Research统计数据图表。从2005年到2015年,NAND闪存的晶体管比例由34%增长至近80%。

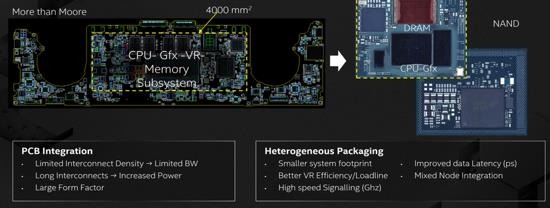

在2019年的Semicon大会上,英特尔公司主办了一场关注半导体封装的特别活动。随着传统半导体规模的不断放缓,芯片之间的具体封装与通信方法,成为满足2020年这十年当中大数据、物联网以及人工智能等技术带来的爆炸性需求增长的关键。目前,大部分高电流封装设计的主要特征,在于采用更大的封装级集成规模与SoC拆分。英特尔公司目前的部分重要目标在于开发新型技术,从而在封装中将不同芯片对接起来以形成等同于SoC单片的功能。

目前关于封装技术的关注焦点包括:超薄/小尺寸客户产品封装(例如智能手机与可穿戴设备)、强大的交付架构、在使用高速信号时对发热量的控制、芯片互连的密度与间距缩放、以及使用来自多个异构设备来源的多种设计等。下图所示为英特尔方面发布的一份文稿,其中阐述了从传统PCB集成到异构封装(包括DRAM与NAND)的转变。异构封装使得电子元件的物理面积更小、能效更高且性能更强。

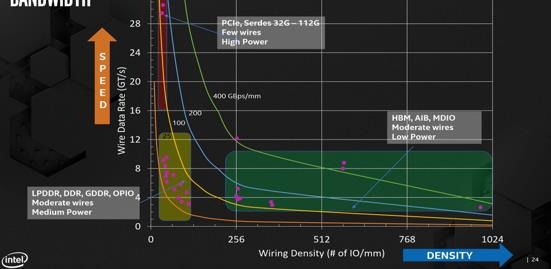

除了缩小集成电路的物理面积之外,目前的封装工艺也越来越薄,这一点往往通过削薄并堆叠晶片、并在芯片背面构建某些结构的方式实现。此外,性能选项也在不断增加。所谓带宽密度,是指线数据速率乘以所谓布线密度(每毫米IO数值)所得出的结果,并以GBps/mm表示。下图展示了几种设备类型(特别是存储设备)的带宽密度。

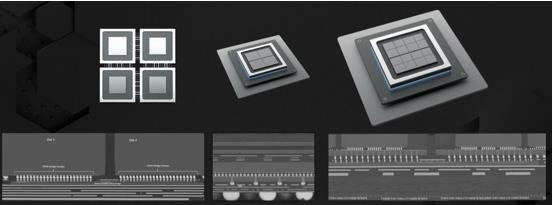

目前业界正从典型的有机封装(FCGBA)转向更为先进的超密度GCBGA(WIP),后者在有机基板上利用新型设备与光刻工艺以将IO/mm/层从23至48提升至64至256。采用嵌入式芯片的方法,代工厂能够在EMIB高密度板的封装之内采用密度极高的布线,其IO密度可以达到256至1024 IO/mm/层。此外,英特尔公司也一直在探索其3D芯片堆叠版本,并将此命名为Feveros。如下图所示(含横截面),Feveros可以与EMIB结合使用。

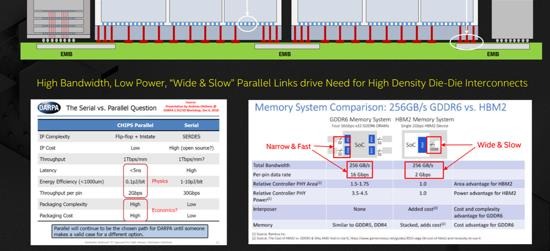

缩短处理器与存储器之间的距离能够显著提高性能,这种设计在降低延迟以及提高功率效率方面体现得尤其突出。通过这种方式,我们不再需要将大量功率用于数据在处理器与存储器之间的往来传输身上。英特尔公司致力于通过Feveros芯片堆叠等方式实现存储器与处理器的集成。目前,高带宽、低功率密集并行链路(例如高带宽存储器,简称HBM)的广泛采用正在推动市场对于晶片间高密集互连的需求。

通过下图可以看出,并行互连HBM能够带来远优于串行互连DDR接口的低延迟与低功耗水平。这种高密度并行互连方法主要受到布线密度、链路长度、线宽、线与线之间间隔以及线之间电介质性质等因素的影响。

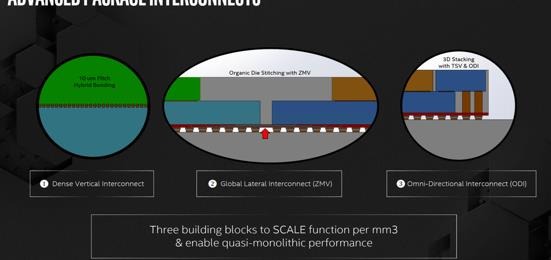

下图总结了几种能够使处理器与存储器尽可能贴近的多芯片互连方法,分别为高密度垂直互连、全校准通孔(ZMV)横向互连以及全向互连(ODI)。

绝大多数半导体晶体管能够支持多种内存技术,特别是DRAM与NAND。而英特尔方面在本届Semicon大会上展示的各项高级封装技术,则能够进一步在内存与处理系统之间建立起高性能连接。

本文章选自《AI启示录》杂志,阅读更多杂志内容,请扫描下方二维码